集成電路設(shè)計中的IP技術(shù)及其產(chǎn)業(yè)發(fā)展特點

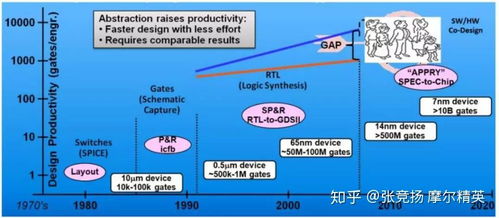

在當(dāng)今高度復(fù)雜化和分工精細(xì)化的半導(dǎo)體產(chǎn)業(yè)中,集成電路設(shè)計已從傳統(tǒng)的從頭到尾全流程自主開發(fā),轉(zhuǎn)變?yōu)榇罅繌?fù)用已驗證的成熟功能模塊,即IP(Intellectual Property Core,知識產(chǎn)權(quán)核)。IP技術(shù)已成為推動集成電路設(shè)計效率提升、成本降低和產(chǎn)品快速上市的關(guān)鍵驅(qū)動力,并深刻塑造了IC設(shè)計產(chǎn)業(yè)的生態(tài)與發(fā)展模式。

IP技術(shù)的核心內(nèi)涵與分類

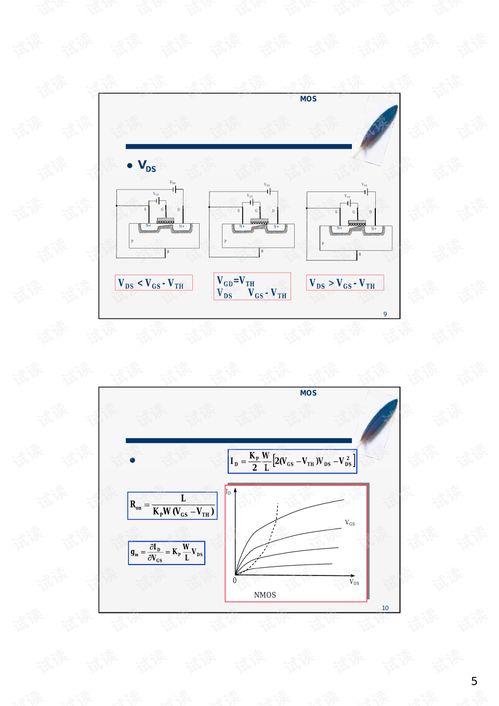

IP核是指在集成電路設(shè)計中,那些經(jīng)過預(yù)先設(shè)計、驗證、功能與性能相對獨立,可以被重復(fù)使用的電路模塊或設(shè)計數(shù)據(jù)。根據(jù)其交付形態(tài)和可定制程度,主要分為三類:

- 軟核(Soft Core):通常以可綜合的硬件描述語言(如Verilog、VHDL)源代碼形式交付。設(shè)計靈活度高,便于根據(jù)特定工藝和需求進(jìn)行修改優(yōu)化,但性能、面積和功耗存在不確定性,且涉及知識產(chǎn)權(quán)保護(hù)較復(fù)雜。

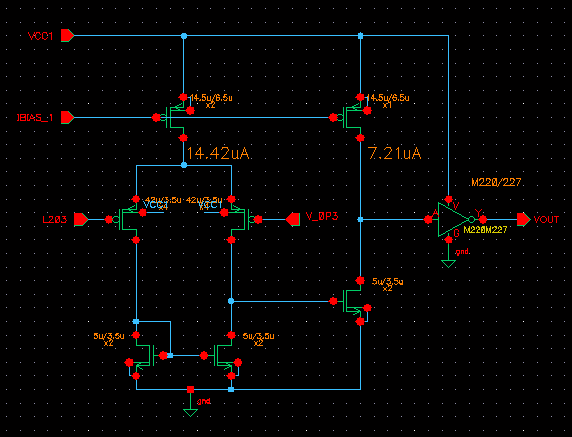

- 固核(Firm Core):以門級網(wǎng)表(Netlist)形式交付。它在結(jié)構(gòu)、面積和時序上經(jīng)過了預(yù)優(yōu)化,比軟核有更確定的表現(xiàn),但可移植性略差于軟核。

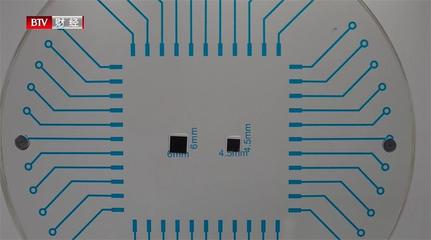

- 硬核(Hard Core):以經(jīng)過物理設(shè)計、針對特定工藝的版圖(GDSII)形式交付。其性能、面積和功耗高度確定且優(yōu)化至最佳,但完全不可修改,工藝綁定性強(qiáng)。

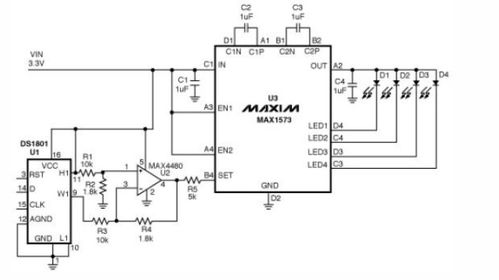

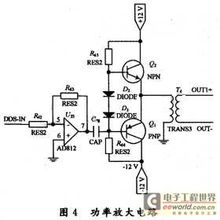

從功能上,IP核涵蓋了處理器內(nèi)核(如ARM Cortex系列、RISC-V)、接口協(xié)議(如USB、PCIe、DDR)、模擬模塊(如PLL、ADC/DAC)以及基礎(chǔ)單元庫(Standard Cell Library)和存儲器編譯器(Memory Compiler)等,構(gòu)成了現(xiàn)代SoC(片上系統(tǒng))的“積木塊”。

IP技術(shù)在集成電路設(shè)計中的關(guān)鍵作用

- 提升設(shè)計效率,縮短上市時間:復(fù)用成熟的IP核,避免了從零開始的重復(fù)設(shè)計、驗證和物理實現(xiàn)工作,能將設(shè)計團(tuán)隊的精力和資源集中于實現(xiàn)產(chǎn)品的差異化和核心創(chuàng)新功能上,從而將產(chǎn)品開發(fā)周期從數(shù)年縮短至數(shù)月。

- 降低設(shè)計難度與風(fēng)險:復(fù)雜IP(如高性能處理器、高速SerDes)的設(shè)計需要極高的專業(yè)知識和經(jīng)驗。使用經(jīng)過硅驗證(Silicon-Proven)的IP,可以顯著降低技術(shù)門檻和流片失敗的風(fēng)險,保障芯片的功能正確性和可靠性。

- 優(yōu)化系統(tǒng)性能與成本:專業(yè)IP供應(yīng)商的持續(xù)投入使其產(chǎn)品在性能、功耗、面積(PPA)上往往優(yōu)于一般設(shè)計公司的自研成果。通過選用最優(yōu)IP組合,可以在系統(tǒng)層面實現(xiàn)更好的PPA平衡,降低單芯片成本。

IP產(chǎn)業(yè)的獨特發(fā)展特點

IP技術(shù)的興起,催生了一個高度專業(yè)化、分工明確的IP產(chǎn)業(yè),其發(fā)展呈現(xiàn)出以下鮮明特點:

- 產(chǎn)業(yè)高度集中與專業(yè)化分工:全球IP市場呈現(xiàn)寡頭壟斷格局,少數(shù)巨頭(如ARM、Synopsys、Cadence)占據(jù)了絕大部分市場份額。也涌現(xiàn)出眾多在細(xì)分領(lǐng)域(如接口、安全、AI加速)具有獨特技術(shù)的“小而美”的IP公司。IP供應(yīng)商、EDA工具商、芯片設(shè)計公司(Fabless)、晶圓代工廠(Foundry)之間形成了緊密協(xié)作、相互依存的生態(tài)鏈。

- 商業(yè)模式多樣化:IP的授權(quán)模式靈活,主要包括一次性技術(shù)授權(quán)費(fèi)(License Fee)和按芯片銷量收取的版稅(Royalty)。訂閱制、成功付費(fèi)(Pay-as-You-Succeed)等新模式也在探索中。開源IP(以RISC-V生態(tài)為代表)的崛起,正挑戰(zhàn)著傳統(tǒng)的商業(yè)授權(quán)模式,促進(jìn)了更低成本、更開放的創(chuàng)新。

- 技術(shù)演進(jìn)驅(qū)動IP持續(xù)創(chuàng)新:隨著半導(dǎo)體工藝向更先進(jìn)節(jié)點(如3nm、2nm)邁進(jìn),以及應(yīng)用領(lǐng)域向人工智能、自動駕駛、高性能計算擴(kuò)展,對IP提出了更高要求。這驅(qū)動著IP技術(shù)本身在超低功耗設(shè)計、Chiplet(芯粒)互連(如UCIe)、高速接口、安全性、可測性等方面不斷創(chuàng)新。先進(jìn)工藝下的IP開發(fā)和驗證成本急劇上升,進(jìn)一步強(qiáng)化了專業(yè)IP供應(yīng)商的地位。

- 知識產(chǎn)權(quán)保護(hù)是生命線:IP產(chǎn)業(yè)的核心資產(chǎn)是知識產(chǎn)權(quán)。完備的法律協(xié)議(NDA、授權(quán)合同)、嚴(yán)格的技術(shù)保護(hù)措施(如加密、水印)以及健康的行業(yè)自律,是IP交易和產(chǎn)業(yè)可持續(xù)發(fā)展的基石。

- 與EDA和制造工藝深度綁定:IP,尤其是硬核和標(biāo)準(zhǔn)單元庫,其性能和可靠性嚴(yán)重依賴于特定的EDA設(shè)計流程和晶圓廠工藝。因此,領(lǐng)先的IP供應(yīng)商通常與EDA巨頭和頂級Foundry建立戰(zhàn)略聯(lián)盟,確保IP在目標(biāo)工藝上達(dá)到最佳效果。

與展望

IP技術(shù)及其產(chǎn)業(yè)是現(xiàn)代集成電路設(shè)計的基石。它不僅是一種提高效率的工具,更是一種重構(gòu)設(shè)計流程、重塑產(chǎn)業(yè)格局的范式。隨著芯片復(fù)雜度持續(xù)提升和異構(gòu)集成(如Chiplet)成為趨勢,IP的角色將從“功能模塊”進(jìn)一步演化為“系統(tǒng)子系統(tǒng)”或“芯粒”。IP產(chǎn)業(yè)將在標(biāo)準(zhǔn)化(如接口協(xié)議)、安全性、可靠性和驗證復(fù)雜度方面面臨更大挑戰(zhàn),同時也將在推動芯片設(shè)計民主化、支撐萬物智能時代多樣化芯片需求方面發(fā)揮更為核心的作用。對于集成電路設(shè)計公司而言,如何構(gòu)建高效的IP選型、集成和管理策略,平衡自主可控與外部采購,將成為其核心競爭力的重要組成部分。

如若轉(zhuǎn)載,請注明出處:http://m.jzjsh.cn/product/5.html

更新時間:2026-03-15 14:29:41